# SERIAL VOICE SRAM (128K · 1 BIT)

# GENERAL DESCRIPTION

The W55206B is a normal speed, low power CMOS static RAM organized as 128K  $\times$  1 bit that operates on a single 5V power supply. Manufactured using Winbond's high performance CMOS technology, the W55206B is designed for extensive use in voice recording applications.

### **FEATURES**

- Single 3.6V to 5.5V power supply

- Low power consumption

- Fully static operation

- · Low data retention voltage

- Easy to cascade

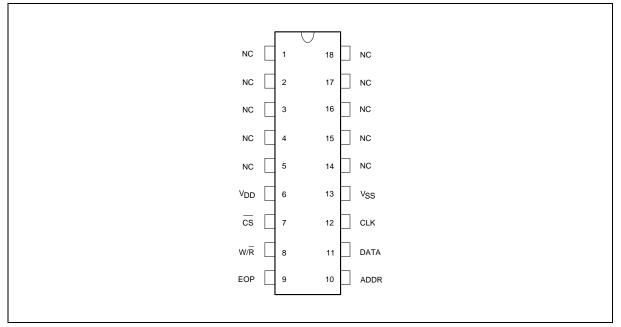

### **PIN CONFIGURATION**

#### **PIN DESCRIPTION**

| NO. | PIN | I/O | DESCRIPTION                                                                                                          |

|-----|-----|-----|----------------------------------------------------------------------------------------------------------------------|

| 6   | Vdd | PWR | Positive power supply                                                                                                |

| 7   | CS  | I   | Chip-inhibit for $\overline{CS} = 1$ ; chip-select for $\overline{CS} = 0$ or open (with internal pull-low resistor) |

#### Pin Description, continued

| NO. | PIN  | I/O | DESCRIPTION                                                                           |  |  |  |

|-----|------|-----|---------------------------------------------------------------------------------------|--|--|--|

| 8   | W/R  | I   | Write-in control for $W/\overline{R} = 1$ , read-out control for $W/\overline{R} = 0$ |  |  |  |

| 9   | EOP  | 0   | End signal output                                                                     |  |  |  |

| 10  | ADDR | I   | Clock input for start address                                                         |  |  |  |

| 11  | DATA | I/O | Bidirectional data pin                                                                |  |  |  |

| 12  | CLK  | I   | Clock input for address increment                                                     |  |  |  |

| 13  | Vss  | PWR | Ground                                                                                |  |  |  |

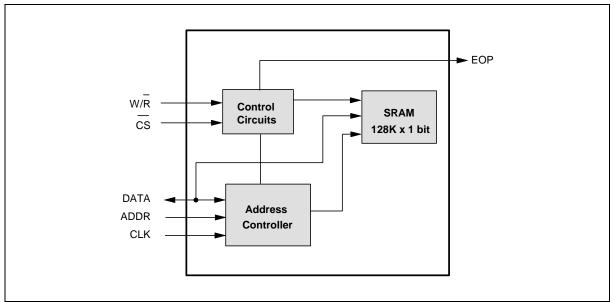

# **BLOCK DIAGRAM**

# FUNCTIONAL DESCRIPTION

• TRUTH TABLE

| CS | W/R | W/R MODE DATA PIN |          | VDD CURRENT |  |

|----|-----|-------------------|----------|-------------|--|

| Н  | Х   | Not selected      | High Z   | ISB         |  |

| L  | Н   | Write             | Data in  | IOP         |  |

| L  | L   | Read              | Data out | IOP         |  |

• When the chip is unselected, the  $W/\overline{R}$  signal will be transmitted to the EOP pin.

• Before a read or write operation, the address counter must be reset by sending an ADDR pulse and setting DATA = 0.

#### **Winbond** Electronics Corp.

- After power on, the read operation is disabled. A read operation may be performed only after a write operation is completed.

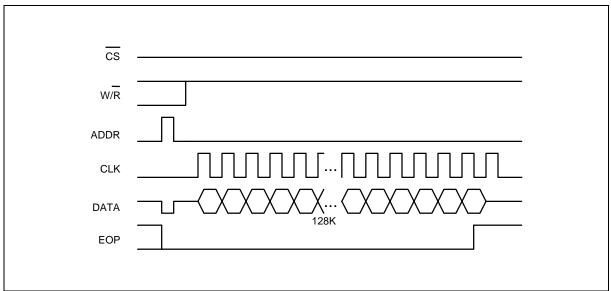

- In write-in operation, the EOP signal will change from low to high and remain high when the final address of the chip is encountered. It will change to low again with the next ADDR pulse.

- In read-out operation, the EOP pin will generate one pulse signal when the final address of the SRAM chip is encountered.

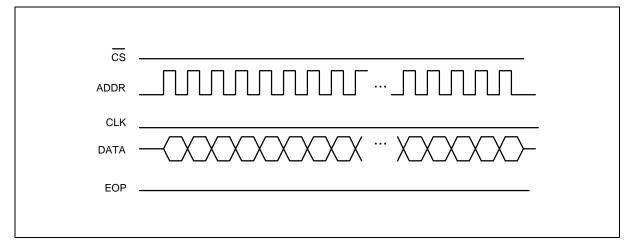

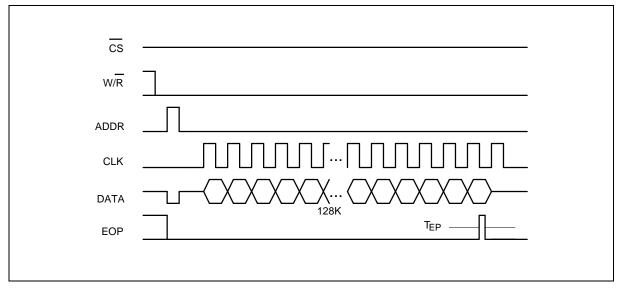

The timing of the loading start address for write-in/read-out operations is shown below:

• Load start address for write-in/read-out operations:

• Write-in operation:

# W55206B

• Read-out operation:

• No operation (standby)

| cs  |      |  |

|-----|------|--|

| W/R | <br> |  |

| EOP |      |  |

|     |      |  |

### **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER             | SYMBOL  | RATING               | UNIT |

|-----------------------|---------|----------------------|------|

| Supply Voltage        | VDD-VSS | -0.3 to +5.5         | V    |

| Input Voltage         | Vin     | Vss -0.2 to VDD +0.2 | V    |

| Output Voltage        | Vo      | VSS to VDD           | V    |

| Operating Temperature | Topr    | 0 to +70             | °C   |

| Storage Temperature   | Tstg    | -55 to +150          | °C   |

Note: Exposure to conditions beyond those listed under Absolute Maximum Ratings may adversely affect the life and reliability of the device.

# **DC CHARACTERISTICS**

$TA = 25^{\circ} \text{ C}, \text{ Vdd} = 5.0 \text{ V}, \text{ Vss} = 0.0 \text{ V}$

| PARAMETER                                        | SYMBOL | CONDITIONS                                          | LIMIT |      | UNIT |    |

|--------------------------------------------------|--------|-----------------------------------------------------|-------|------|------|----|

|                                                  |        |                                                     | MIN.  | TYP. | MAX. |    |

| Operating Voltage                                | Vdd    | -                                                   | 3.6   | 5.0  | 5.5  | V  |

| Operating Current                                | IOP    | Fc = 1 MHz                                          | -     | -    | 15   | mA |

| VDD for Data Retention                           | Vdr    | $\overline{\text{CS}} \ge \text{VDD} - 0.2\text{V}$ | 2.4   | -    | 5.5  | V  |

| Data Retention Current                           | Idddr  | $VDD \ge 3V, \ \overline{CS} \ge 2.8V$              | -     | -    | 10   | μA |

| Standby Current                                  | ISB    | -                                                   | -     | 2    | 10   | μA |

| Input Voltage (for ADDR,                         | Viн    | -                                                   | 2.8   | -    | 6.0  | V  |

| CLK, W/ $\overline{R}$ and $\overline{CS}$ pins) | VIL    | -                                                   | -0.5  | -    | +0.8 |    |

| Input Current (for CS)                           | Ін     | VI = 5.0V                                           | -     | -    | 5    | μA |

| Output Current (for EOP)                         | Юн     | Vo = 4.0V                                           | 4     | 6    | -    | mA |

|                                                  | IOL    | Vo = 0.8V                                           | -4    | -8   | -    |    |

# AC CHARACTERISTICS

Ta =  $25^{\circ}$  C, VDD = 5.0V, Vss = 0.0V

| PARAMETER                                        | SYMBOL | CONDITIONS | MIN. | TYP | MAX. | UNIT |

|--------------------------------------------------|--------|------------|------|-----|------|------|

| Clock Frequency (for CLK and ADDR)               | FC     | -          | -    | -   | 1    | MHz  |

| Data Hold Time                                   | Тwн    | Write mode | 0    | -   | -    | nS   |

| Data Hold Time                                   | Trh    | Read mode  | 0    | -   | -    | nS   |

| Data Hold Time (for ADDR)                        | Тан    | -          | 0    | -   | -    | nS   |

| Data Access Time                                 | Tra    | Read mode  | -    | -   | 80   | nS   |

| Data Setup Time                                  | Tws    | Write mode | 250  | -   | -    | nS   |

| Data Setup Time (for ADDR)                       | TAS    | -          | 250  | -   | -    | nS   |

| EOP Pulse Width (for ADDR)                       | Tep    | Read mode  | 100  | -   | -    | nS   |

| High Level Duration of Clock<br>for CLK and ADDR | Тн     | -          | 400  | -   | -    | nS   |

| Low Level Duration of Clock<br>for CLK and ADDR  | ΤL     | -          | 600  | -   | -    | nS   |

| W/R Signal Setup Time for Write Mode             | TSUR   | -          | 300  | -   | -    | nS   |

| W/R Signal Setup Time for Write Mode             | Tsuw   | -          | 300  | -   | -    | nS   |

| Time Width Between ADDR<br>and CLK Clock         | TD     | -          | 1    | -   | -    | μS   |

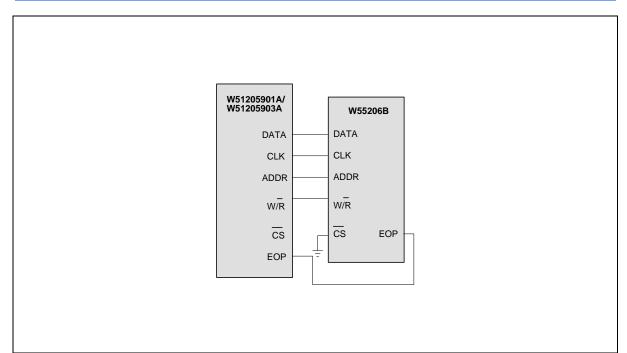

# TYPICAL APPLICATION CIRCUIT (For reference only)

# W55206B

\* W51205901A/W51205903A substrate connected to Vss for C.O.B.

\* W55206B substrate connected to VDD for C.O.B.

#### **Headquarters**

No. 4, Creation Rd. III, Science-Based Industrial Park, Hsinchu, Taiwan TEL: 886-3-5770066 FAX: 886-3-5792697 http://www.winbond.com.tw/ Voice & Fax-on-demand: 886-2-7197006

Taipei Office

11F, No. 115, Sec. 3, Min-Sheng East Rd., Taipei, Taiwan TEL: 886-2-7190505 FAX: 886-2-7197502

Winbond Electronics (H.K.) Ltd. Rm. 803, World Trade Square, Tower II, 123 Hoi Bun Rd., Kwun Tong, Kowloon, Hong Kong TEL: 852-27513100 FAX: 852-27552064

Winbond Electronics North America Corp. Winbond Memory Lab. Winbond Microelectronics Corp. Winbond Systems Lab. 2730 Orchard Parkway, San Jose, CA 95134, U.S.A. TEL: 1-408-9436666 FAX: 1-408-9436668

Note: All data and specifications are subject to change without notice.